4 دقیقه

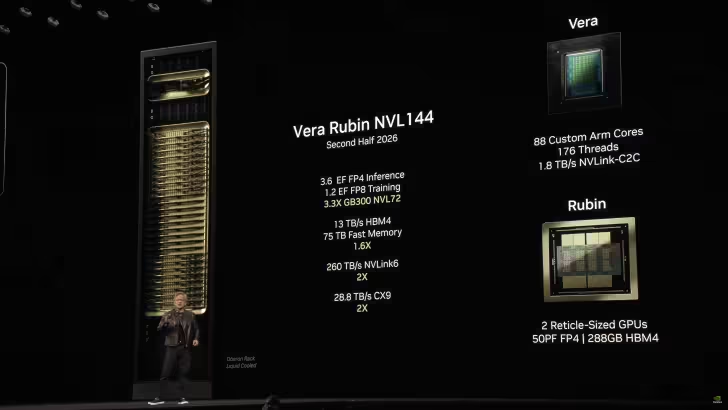

جنسن هوانگ، مدیرعامل NVIDIA، تایید کرده است که شرکت فعالانه معماری هوش مصنوعی نسل بعدی خود به نام روبین را در TSMC آماده میکند. بهطور داخلی روبین بهعنوان گامی انقلابی برای محاسبات توصیف شده و بازطراحی از پایهٔ پشتهٔ دیتاسنتر انویدیا را نشان میدهد — از حافظه و گرهٔ فرآیندی تا بستهبندی و اتصالها. هوانگ فاش کرد که انویدیا قبلاً شش چیپ روبین را تیپآوت کرده که اکنون در کارخانههای TSMC قرار دارند و برای تولید آزمایشی آماده میشوند.

آنچه جنسن هوانگ اعلام کرد

در جریان سفرش به تایوان، هوانگ به رسانههای محلی گفت که روبین «بسیار پیشرفته» است و شش چیپ جداگانهٔ روبین تیپآوت شده و به TSMC تحویل داده شدهاند. این چیپها شامل دیاییسیهای جدید CPU و GPU و همچنین سیلیکون تخصصی برای مقیاسپذیری و ارتباطات هستند. این اعلام نشاندهندهٔ بازنگری گستردهٔ پلتفرم است، نه یک بهروزرسانی جزئی.

چیپهای تأییدشده در تیپآوت

- دیای پردازندهٔ اختصاصی

- GPU نسل بعد (انتظار میرود خانوادهٔ R100 باشد)

- سوییچ NVLink برای مقیاسپذیری multi-GPU با پهنای باند بالاتر

- پردازشگر فوتونیک سیلیکونی برای ورودی/خروجی نوری

- دیایهای رابط/بریج اضافی برای پشتیبانی از یکپارچهسازی چیپلت

- چیپهای منطق بستهبندی و سوییچ

ویژگیها و نوآوریهای فنی

روبین چندین ارتقای اثرگذار برای محاسبات هوش مصنوعی دارد. انویدیا قصد دارد از حافظهٔ HBM4 برای تغذیهٔ GPUهای R100 استفاده کند، که گامی مهم فراتر از استاندارد فعلی HBM3E است. طراحی از فرایند N3P تیاسامسی در ردهٔ 3nm و بستهبندی پیشرفتهٔ CoWoS-L بهره خواهد برد. نکتهٔ مهم آن است که روبین معماری چیپلت را اتخاذ کرده — که برای انویدیا در این مقیاس نخستین است — و به طرح ریتیکل 4x در مقابل تقریباً 3.3x در بلکول منتقل میشود، که امکان نواحی ترکیبی بزرگتر و مقیاسپذیری مدولارتر را فراهم میآورد. افزودن پردازشگر فوتونیک سیلیکونی و سوییچ NVLink برای مقیاسپذیری نشاندهندهٔ تمرکز بر اتصال با پهنای باند بالا و تأخیر کم برای بارهای کاری توزیعشدهٔ هوش مصنوعی است.

مقایسهها: روبین در برابر بلکول و هاپر

جایی که بلکول اولترا (GB300) نمایانگر اوج نزدیکمدت در نقشهٔ راه فعلی انویدیا بود، روبین هدفش جهشی نسلگونه مشابه آن چیزی است که هاپر پیشتر ارائه داد. تغییر روبین به چیپلت، HBM4، N3P و بستهبندی CoWoS-L نشانگر بهبود در عملکرد، بازدهٔ انرژی و مقیاسپذیری در کارهای آموزش و استنتاج است. تغییرات معماری عمیقتر از یک بهروزرسانی سادهٔ گرهٔ فرآیندی است — آنها معماری حافظه، بستهبندی فیزیکی و توپولوژی اتصال را در بر میگیرند.

مزایا و موارد استفاده

روبین برای آموزش در مقیاس بزرگ، مدلهای زبان عظیم و محاسبات با کارایی بالا که در آن پهنای باند حافظه و ارتباط بین نودها عامل محدودکنندهاند، بهینه شده است. فوتونیک سیلیکونی و سوییچ NVLink برای مقیاسپذیری روبین را برای هایپرسکالرها و خوشههای سازمانی هوش مصنوعی که به fabric متراکم و با تأخیر کم نیاز دارند، جذاب میکند. رویکرد چیپلت همچنین میتواند نرخ بازده (yield) را بهبود دهد و زمان ورود به بازار را برای انواع SKUهای هدفگیریشده به آموزش، استنتاج و سرورهای شتابدادهشدهٔ لبه تسریع کند.

اهمیت بازار و جدول زمانی

با توجه به تیپآوت و آغاز تولید آزمایشی در TSMC، رونمایی تجاری روبین بهطور موقت در بازهٔ 2026–2027 پیشبینی میشود، که بستگی به تاییدها و افزایش بازده دارد. برای ارائهدهندگان ابری، سازندگان OEM و فروشندگان زیرساخت هوش مصنوعی، روبین نمایانگر یک گرهٔ راهبردی است: میتواند معیارهای عملکرد در بازار سرورهای هوش مصنوعی را بازتنظیم کند و دور جدیدی از نوسازی سختافزار در دیتاسنترها را ایجاد نماید.

نتیجهگیری

روبینِ NVIDIA به نظر میرسد که قرار است نقطهٔ عطفی در معماری باشد: ترکیب حافظهٔ HBM4، فرایند 3nm تیاسامسی، مدولاریتۀ چیپلت، بستهبندی CoWoS-L و I/O نوری برای ارائهٔ پلتفرمی پیشرفته برای هوش مصنوعی و HPC. با شش تیپآوت که уже در TSMC قرار دارند، صنعت با دقت تولید آزمایشی را دنبال خواهد کرد تا روبین به احتمال زیاد در بازهٔ 2026–2027 عرضه شود.

منبع: wccftech

ارسال نظر